# 3-D Solenoid Inductor Analysis in a 0.13 μm Digital CMOS Technology

Chul Nam<sup>1</sup> <sup>1</sup>R&D Center/Siliconharmony, Seong Nam-Si, Korea Email: bhkim@cu.ac.kr

Byeungleul Lee<sup>2</sup>, Hyeon Cheol Kim<sup>3</sup>, Jinseok Kim<sup>4</sup>, Dong Wook Chang<sup>5</sup>, and Bonghwan Kim<sup>6</sup>,

<sup>2</sup>Mechatronics Engineering, Korea University of Technology and Education, Chungnam, Korea

Electrical Engineering, University of Ulsan, Ulsan, Korea

<sup>4</sup>Center for Bionics, Biomedical Research Institute, Korea Institute of Science and Technology, Seoul, Korea

<sup>5</sup> Chemical Systematic Engineering, Catholic University of Daegu, Gyeongbuk, Korea

<sup>6</sup>Electronics Engineering, Catholic University of Daegu, Gyeongbuk, Korea

Email: bhkim@cu.ac.kr

*Abstract*—This paper presents the analysis of a small-area on-chip solenoid inductor using the 0.13µm digital CMOS process. The on-chip solenoid inductor is vertically constructed using metal and via layers with a horizontal scalability. This gives the advantage of occupying a small area due to its 3-D structure compared to a spiral inductor. The electrical characteristics of the solenoid inductor have been analyzed by employing 3-D EM simulation. The proposed equivalent model of the solenoid inductor is introduced to get the insight of the scalability so that the selection of the inductance is simply choosing the number of turns. This small area solenoid inductor can be good candidate for LC type VCO for GHz PLL in the standard CMOS process with saving die cost.

*Index Terms*—solenoid inductor, Voltage Controlled Oscillator, EM simulation

## I. INTRODUCTION

As the recent remarkable growth in the digital CMOS technology has reached several GHz in the  $f_t$  frequency, many studies have been done regarding digitally controlled oscillator (DCO)s operating in the several gigahertz range [1]-[2]. However, the spiral type inductor in the DCOs is still the one traditionally used in RF process and so it suffers from a low quality factor and occupies a large area, impacting upon the low processing cost desired for the digital CMOS process. In addition, circuit designers have to face the challenges in designing the spiral inductor by oneself and take responsibility for its performance.

A solenoid inductor implementation has been studied in [3], which mainly uses micro electro mechanical systems (MEMS) technology. By virtue of the good conductivity of copper, the electroplated inductor has a high quality factor and an inductance of a tenth of nH. [4]. However, the post MEMS processing requires the additional mask steps and increases the processing cost. Prior to 0.13  $\mu$ m CMOS process, the poor conductivity of Al CMOS process has adapted a thick metallization method of interconnection in order to reduce the series resistance of inductor. For example, in a LC type voltage controlled oscillator (VCO) in 0.18 $\mu$ m RF process, the spiral inductor uses top metal with thickness of 3  $\mu$ m.

Since CMOS technology has started to adopt Cu metallization below 0.13  $\mu$ m process, it opens the possibility of implementing a low series resistance inductor in LC type VCO. Unfortunately, the large area planar spiral inductor is still used in the digital CMOS process.

In this paper, a solenoid inductor using metal and via stacking is proposed and its electrical characteristics are evaluated in terms of inductance and quality factor using 3D-EM simulation. In the long run, the solenoid inductor could be used for LC-type VCO in the standard CMOS process. Two types of inductors according to the different dimension have been implemented and measured its characteristics using a HP E4440A. The measured S-parameters were used in analyzing the proposed equivalent lumped model and the parameter optimization.

## II. ON-CHIP SOLENOID INDUCTOR DESIGN

## A. Solenoid Structure

Generally, a spiral inductor is fabricated using the planar CMOS process. Thus, the magnetic flux of the spiral inductor penetrates the substrate with its axis perpendicular to the wafer surface. As a result, the spiral inductor suffers from a low quality factor due to the substrate loss.

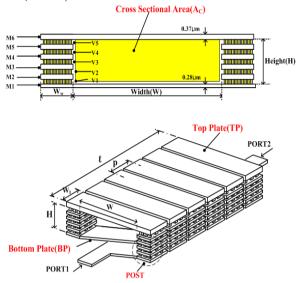

On the contrary, the solenoid inductor shown in Fig. 1 is built by metal and via interconnection and moreover, its axis is parallel to the substrate. This makes the solenoid inductor less susceptible to the substrate losses due to the eddy current. In Fig. 1, the bottom plate is represented by M1 and top plate by M6. The posts are

Manuscript received December 1, 2013; revised March 11, 2014.

connected between the top plate and the bottom plate by Vias (V1-V5).

Figure 1. A structure of the solenoid inductor.

In general macro-scale, the solenoid inductance is expressed in terms of its dimension.

$$L_S = \frac{4\pi \times 10^{-7} \times N^2 \times A_c}{N \times p} \tag{1}$$

where N is the number of turns, Ac is the cross-sectional area that the magnetic flux is crossing; p is the pitch between each turn.

Since the cross area (Ac) is the width (W) and the height (H) and the maximum height is limited by the process technology, the inductance is proportional to the width and the number of turns as Eq. 2.

$$L_{S} \propto W \times N \tag{2}$$

The series resistance (Rs), which directly affects the quality factor by  $Q = \frac{\omega \cdot L_s}{R_s}$ , will be increased due to the skin effect [5] and the proximity effect with an increasing frequency. As the proximity effect from the conductor moves farther from the adjacent turns, it can be neglected and so the approximation of Rs is given by;

$$R_s = R_{dc} \frac{t}{\delta \cdot (1 - e^{\frac{-t}{\delta}})}$$

(3)

$$R_{dc} = \rho_{\Box} \cdot \frac{2N(W+2W_W)}{W_l} \tag{4}$$

$$\delta = \sqrt{\frac{\rho}{\pi \mu f}} \tag{5}$$

where *t*,  $W_W$  and  $W_l$  represent the metal thickness, the post width and the post length, respectively;  $\rho$ ,  $\mu$  and *f* are the resistivity of the copper, the permeability of the air and the operating frequency, respectively. Considering a greater than 5GHz operating frequency, the skin depth is about 0.94 $\mu$ m which is larger than the top metal thickness 0.9 $\mu$ m in 0.13 $\mu$ m digital CMOS process. Thus, ignoring the skep effect, the series resistance, *Rs* becomes 1.2 *R*<sub>dc</sub>. Then Rs can be rewritten as

$$Q = 0.833 \frac{\omega \cdot L_S}{R_{dc}} \tag{6}$$

In addition, the width of the solenoid (W) is larger than the post width, ( $W_W$ ) and length ( $W_l$ ). Rdc is proportional to N • W. the quality factor is also only inversely proportional to N • W as;

$$Q \approx \frac{1}{W \cdot N} \tag{7}$$

From the Eq. (2) and Eq. (7), we can extract the design parameters of the solenoid inductor as W and N. These parameters give insights to the rule of thumb of design the solenoid inductor. However, it is not sufficiently explain the exact performance for circuit simulation when it comes to, for example, LC type VCO using the solenoid inductor so that the EM simulation is required.

## B. EM Simulation

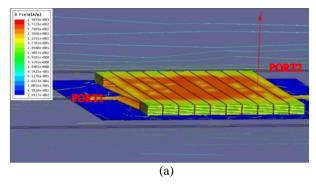

Figure 2. (a) HFSS simulation result of solenoid inductor (b) Design Type I: W=40µm, and (c) Type II: W=60µm.

Fig. 2(a) shows the EM simulation result, H-field from HFSS [6] simulation. For EM simulation, the input excitation is applied to PORT 1 and PORT 2 terminals. The EM simulation gives also its result in S-parameters. Then, the inductance of quality factor of the inductor is determined uniquely from the Y-parameters converted from the S-parameters by;

$$L_{11} = \frac{-1}{2\pi \cdot f \cdot im(Y_{11})}, Q_{11} = \frac{im(Y_{11})}{Re(Y_{11})}$$

(8)

where  $L_{II}$  and  $Q_{II}$  are the inductance and quality factor looking at port1, im( $Y_{II}$ ) and Re( $Y_{II}$ ) are the imaginary part and real part of  $Y_{II}$ .

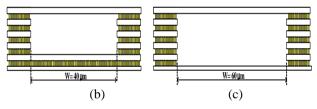

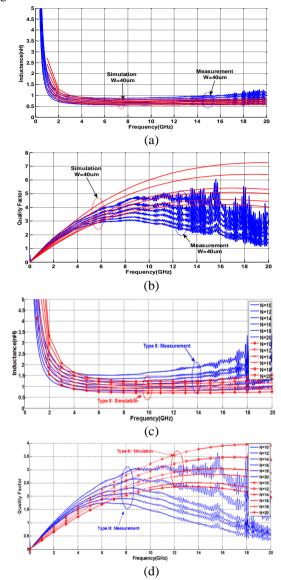

The proposed solenoid inductors have two types according to the width (W), type I: 40  $\mu$ m (Fig. 2(b)) and type II: W=60 $\mu$ m (Fig. 2(c)). Notably, type I has bottom plates stacking metal1 (M1) and metal2 (M2) in order to reduce the series resistance. Each type has a varied number of turns (N) from 10 to 20 by even number increments. Fig. 3 shows the results of the inductance (L<sub>11</sub>) and quality factor (Q<sub>11</sub>) from the HFSS simulation.

From Fig. 3(a), the inductance is range from 0.6 to 0.9 nH for type I and from 0.8 to 1.5 nH for type II and the quality factor has 7 and 4 in maximum for type I and type II respectively. It is clear that the inductance increases according to Ws from 40  $\mu$ m to 60  $\mu$ m and Ns from 10 to 20 and the quality factor decreases according to W and N as Eq. (2) and Eq. (7). Since the quality factor is directly affected by the total length, that is Ls, the type I inductor with stacked bottom plate, has a higher quality factor than type II.

Figure 3. (a) Inductance and (b) Quality factor from the simulation of type I (W=40 μm) and type II (W=60 μm).

C. Inductor Measurement

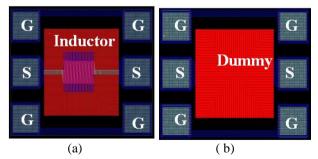

Figure 4. The layout of (a) solenoid inductor and (b) open pad for deembedding.

Solenoid inductor was fabricated in 0.13 µm digital CMOS process and measured using on-chip probing. With a network analyzer (N5230A), a cascade microtech probe station and cascade microtech ground-signal (GSG) probes, the two port S-parameters of the solenoid inductor were measured range from 100 MHz to 20 GHz. The pad de-embedding was performed by subtracting out Y-parameters of open pad from Y-parameters of the solenoid inductor. Fig. 4 shows an inductor layout with

probe pattern and open pad used for pad de-embedding. The measured inductance and quality factor after deembedding are shown along with the simulation results in Fig. 5.

Figure 5. (a) and (c): Measured inductance (Blue) vs. the simulated inductance (Red) (b) and (d): the measured Q-factor (Blue) vs. the simulated Q-factor (Red) of type I and type II inductor respectively.

#### **III. SOLENOID INDUCTOR MODELING**

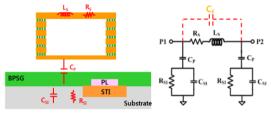

In general, the spiral inductor has been characterized using " $\pi$ " model [7]-[8]. The solenoid inductor can also use this " $\pi$ " model ignoring some parameter. In this paper, a lumped-element circuit from the spiral model was established for the solenoid inductor model as shown in Fig. 6.

In this model,  $R_S$  and  $L_S$  are the series resistance and the inductance, respectively. The capacitance coupling,  $C_f$ which is modeled as a feed forward fringing one between two terminals can be neglected since two terminals are surely separated by the inductor length.  $C_P$  is denoted as the base plate coupling capacitance with the substrate.  $C_{SI}$ and  $R_{SI}$  are the substrate parasitic capacitance and resistance, respectively. With this model, every inductor from type I and type II with number of turns has been optimized over 100 MHz and 20 GHz about the magnitude and phase with the measured de-embedded Sparameters using Agilent ADS [9]. The results are listed in Table I.

Figure 6. The lumped equivalent model for the solenoid inductor.

TABLE I. SUMMARY OF PARAMETERS FOR THE PROPOSED SOLENOID INDUCTOR MODEL

| Model            | # of<br>Turn | L <sub>s</sub> (nH) | $R_{S}(\Omega)$ | C <sub>P</sub> (fF) | $R_{SI}(\Omega)$ | C <sub>SI</sub> (fF) |

|------------------|--------------|---------------------|-----------------|---------------------|------------------|----------------------|

| Type I<br>(40W)  | 10           | 0.50                | 3.52            | 82.5                | 182.4            | 9.95                 |

|                  | 12           | 0.54                | 4.42            | 91.9                | 180.1.           | 14.7                 |

|                  | 14           | 0.59                | 4.95            | 101.0               | 181.9            | 14.4                 |

|                  | 16           | 0.64                | 5.78            | 108.7               | 193.1            | 13.0                 |

|                  | 18           | 0.70                | 5.85            | 114.0               | 169.4            | 10.6                 |

|                  | 20           | 0.75                | 6.71            | 120.0               | 174.4            | 10.9                 |

| Type II<br>(60W) | 10           | 0.68                | 7.27            | 100.2               | 198.5            | 12.7                 |

|                  | 12           | 0.78                | 9.25            | 112.6               | 189.3            | 15.8                 |

|                  | 14           | 0.88                | 11.6            | 122.7               | 181.1            | 16.5                 |

|                  | 16           | 0.99                | 13.4            | 133.0               | 184.9            | 14.5                 |

|                  | 18           | 1.10                | 14.0            | 136.9               | 173.9            | 8.0                  |

|                  | 20           | 1.20                | 16.7            | 142.9               | 167.7            | 7.6                  |

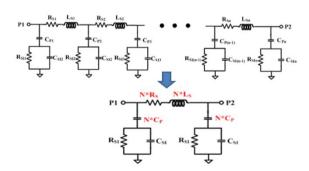

Among these model parameters,  $R_{SI}$  and  $C_{SI}$  are almost constant over design parameters, W and N. L<sub>S</sub>,  $R_S$  and  $C_P$ , however, seems dependent on these design parameters, W and N. Fig. 7 shows each model parameters such as L<sub>S</sub>,  $R_S$  and  $C_P$  for type I and type II have dependency against the number of turns (N). From a structure point of view, each design parameters have a relationship of the width and the height, which can be written as;

$$C_{P2} = C_{P1} * W_2 / W_1 \tag{9}$$

$$L_{s2} = L_{s1}^{*}(W_{2} + H_{2}) / (W_{1} + H_{1})$$

(10)

$$R_{S2} = R_{S1} * (W_2 + H_2) / (W_1 + H_1)$$

(11)

where  $W_1 = 40\mu m$  for type I,  $W_2 = 60\mu m$  for type II,  $H_1$  and  $H_2$  is the height of the post for type I and type II, respectively.

TABLE II. COMPARISON INDUCTOR DIE AREA

| Ref                                | [10]   | [11] | [12]   | [13]     | This Work |

|------------------------------------|--------|------|--------|----------|-----------|

| Process<br>(µm)                    | 0.24   | 0.18 | 0.09   | 0.13-SOI | 0.13      |

| Inductor<br>Type                   | Spiral | Ring | Spiral | Spiral   | Solenoid  |

| Inductor<br>Size(mm <sup>2</sup> ) | 0.053  | -    | 0.020  | 0.212    | 0.013     |

Since the width of the plate is larger than the height of the post, that is W >> H,  $R_{S2}$ ,  $L_{S2}$  and  $C_{P2}$  are approximately 1.2~2.5 times  $R_{S1}$ ,  $L_{S1}$  and  $C_{P1}$ .

Furthermore, each turn of solenoid inductor is repeated in longitude and design parameters can be expressed in terms of N as shown in Fig. 8. Thus these equations are summarized as

$$L_{\rm S}({\rm N}) = 0.048 * {\rm N} + 0.20 \tag{12}$$

$$R_{\rm s}({\rm N}) = 0.765 * {\rm N} + 0.78$$

(13)

$$C_P(N) = 4.132*N+62.17$$

(14)

From these equations, the constants,  $L_S$  (0),  $R_S$  (0) and  $C_P$  (0) come from the parasitic of input terminals.

Figure 7. (a) L<sub>S</sub>.vs. N (b) R<sub>S</sub>.vs. N (c) C<sub>P</sub>.vs. N; subscript of each parameter denotes 1 for type I and 2 for type II.

Figure 8. The proposed unified equivalent model of solenoid inductor.

## IV. CONCLUSIONS

A small area solenoid type inductor was proposed and its electrical characteristics were evaluated by EM simulation. The two types of solenoid inductors were fabricated and compared to the simulation result. Using the proposed unified equivalent model, the design parameters based on the dimension were optimized over high frequency band and linearized by 1st order equation.

The solenoid inductor has small area compared to the prior art as shown table II. This solenoid inductor is expected to use the LC type VCO in gigahertz PLL in the standard CMOS process with saving die cost. Moreover, the scalability by number of turns gives the advantage of choosing the inductance and quality factor by engineer insight.

#### ACKNOWLEDGMENT

This research was supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (2013R1A1A4A01012255).

#### REFERENCES

- [1] R. B. Stazewski and P. Balsar, *All Digital Frequency Synthesizer* in *Deep-Submicron CMOS*, A Jon Wiley & Sons, 2006.

- [2] P. L. Chen, C. C. Chung, and C. Y. Lee, "A portable digitally controlled oscillator using novel varactors," *IEEE Trans. on Circuits and Systems*, vol. 52, no. 5, May 2005.

- [3] J. B. Yoon, B. K. Kim, C. H. Han, E. Yoon, and C. K. Kim, "Surface micro machined solenoid on Si and on-glass inductor for RF applications," *IEEE Electron Device Letter*, vol. 20, no. 9, pp. 487-489, Sep. 1999.

- [4] S. Seok, C. Nam, W. Choi, and K. Chun, "A high performance solenoid-type MEMS inductor," *Journal of Semiconductor Technology and Science*, vol. 1, no. 3, June 2001.

- [5] T. H. Lee, "The design of CMOS radio-frequency integrated circuits," Cambridge, United Kingdon, p. 50, 1998

- [6] ANSYS HFSS. [Online]. Available: http://www.ansys.com

- [7] J. N. Burghartz and B. Rejaei, "On the design of RF spiral inductors on silicon," *IEEE Trans. Electro Devices*, vol. 50, no. 3, pp. 718-729, Mar. 2003.

[8] J. R. Long and M. A. Copeland, "The modeling, characterization

- [8] J. R. Long and M. A. Copeland, "The modeling, characterization and design of monolithic inductors for silicon RF IC's," *IEEE J. Solid-State Circuits*, vol. 32. no. 3, pp. 357-369, Mar. 1997.

- [9] Agilent ADS. [Online]. Available: http://www.agilent.com

- [10] H. R. Rategh, H. Samavati, and T. H. Lee, "A 5GHz 32mW CMOS frequency synthesizer with an injection locked frequency divider,"

- [11] R. Tao and M. Berroth, "The design of 5GHz voltage controlled ring oscillator using source capacitively coupled current amplifier," *IEEE Radio Frequency Integrated Circuits Symposium*, pp. 623-626, 2003.

- [12] B. Soltanian, H. Ainspan, W. Rhee, D. Friedman, and P. Kinget, "An ultra compact differentially tuned 6GHz CMOS LC VCO with dynamic common-mode feedback," *CICC*, pp. 671-674, 2006.

- [13] N. Fong, et al., "A 1-V 3.8-5.7GHz wideband VCO with differentially tuned accumulation MOS varactor for commonmode noise rejection in CMOS SOI technology," *IEEE Transactions on Microwave Theory and Techniques*, vol. 51, no. 8, pp. 1952-1959, 2003.

Chul Nam Received the BS degree from KAIST, Korea, in 1991, the MS degree from Seoul National University, Korea, in 2001 and Ph.D. degree from KonKuk University, Korea, in 2011. From 1991 to 1997, he worked as mixed analog ASIC engineer at Samsung Electronics. Since 2004, he has been with Siliconharmony where he is now RF/ Analog Project Leader.

**Byeungleul Lee** is an Associate Professor at Korea University of Technology and Education. He received B.S. degree in Electronics Engineering from the Hanyang University and M.S. degree in Electrical and Electronics engineering from Korea Advanced Institute of Technology, in 1989 and 1991 respectively. He obtained his Ph.D. in Electrical Engineering and Computer Science from the Seoul National

University in 2004. From 1991 to 2008, he worked for Samsung Electronics as a principal researcher for MEMS development His research interests include semiconductor transducer and MEMS applications.

Hyeon Cheol Kim received the B.S., M.S. and Ph.D. degrees in electronic engineering from Seoul National University in 1990, 1992 and 1998, respectively. He has worked as a research staff at Samsung Advanced Institute of Technology from 1998 to 2001 and as a senior engineer at Chromux Technologies Inc. from 2001 to 2003. He also worked as a BK21 contract assistant professor in Seoul National University from 2004 to 2006. He

joined the faculty of University of Ulsan in 2008, where he is currently an associate professor in the School of Electrical Engineering. He is a Member of IEEE and a Life Member of IEEK. His research areas include Micromachining, Semiconductor sensors, RF MEMS, integrated MEMS and Packaging.

**Jinseok Kim** received his Ph.D. in electrical engineering from the Seoul National University, Korea, in 2007 and the M.S. degree in materials engineering from University of Southern California, USA, in 1997. He is currently a principal research scientist in Center for Bionics, Bio-medical Research Institute, Korea Institute of Science and Technology (KIST), Seoul, Korea. His research interests are Optical and Multi-

function Neural Probe for Brain, Neural Device for Spinal Cord Injury, Neural Prosthesis for Peripheral Nerve System Injury, Shape Sensor for Minimally Invasive Surgical Robot using Optical FBG Fiber, Piezoelectric Pressure Sensor for 3D Force Feedback Sensing, and Neural Stem Cell Spheroid for Cell Transplantation Therapy.

**Dong Wook Chang** is an Assistant Professor and Department Chair of Chemical Systematic Engineering at the Catholic University of Daegu, South Korea. He obtained his PhD in Materials Engineering at the University of Dayton in 2007 under the guidance of Prof. Liming Dai. Prior to taking up his current position, he worked for two years as a Senior Researcher at Samsung Total Petrochemicals Company and another two years

as a Research Assistant Professor at the Interdisciplinary School of Green Energy at the Ulsan National University of Science and Technology(UNIST). His research interests include the synthesis and functionalization of conjugated molecules and carbon nanomaterial's for optoelectronic and renewable-energy applications.

**Bonghwan Kim** received the B.S. degree in electronics engineering from the Kyungpook National University, Daegu, Korea, and M.S. and Ph. D. degrees in Electrical Engineering and Computer Science from the Seoul National University, Seoul, Korea, in 1996, 1999, and 2005 respectively. From 2001 to 2005, he was a founder and the president of the ICMEMS Inc., Seoul, Korea. From 2005 to 2007, he was a

principal engineer with UniTest Inc.,where he developed a MEMS probe card. In 2008, he moved to the University of Illinois at Urbana-Champaign and joined the Shannon Group as a post-doctoral research associate. Since 2009, he has worked for Catholic University of Daegu, Gyeongsan, Gyeongbuk, Korea. His current research activities include design and fabrication of MEMS device such as micro cantilever, actuators and MEMS probe card.